Panduan Inovatif untuk JK Flip-Flops: Menganalisis Jadual Kebenaran, Mekanisme, dan Aplikasi Strategik

Artikel ini meneroka seni bina, operasi, dan pelbagai aplikasi flip-flop JK, bermula dari struktur asas dan hubungan input-output, melalui mekanik operasi terperinci, kepada pelaksanaan strategiknya dalam sistem digital yang kompleks.Wacana ini meluas untuk membezakan antara varian yang dicetuskan dan dicetuskan tahap, menganalisis utiliti masing-masing dalam persekitaran segerak dan tidak segerak.Katalog

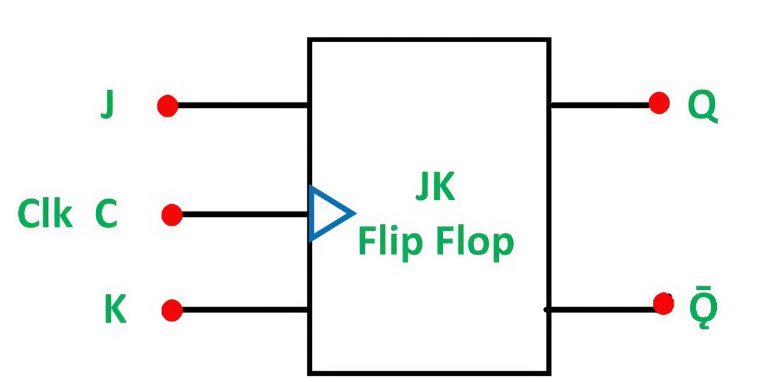

Rajah 1: JK Flip-Flop

Asas JK Flip-Flop

JK Flip-Flop adalah komponen asas dalam elektronik digital, yang direka untuk menyimpan sedikit maklumat.Ia dibina pada flip-flop SR yang lebih mudah dengan menambah maklum balas, yang membantu mencegah kesilapan yang dikenali sebagai "keadaan perlumbaan," di mana output menjadi tidak stabil.

Flip-flop ini mempunyai dua input utama, j (set) dan k (reset), dan dua output: q dan pelengkapnya, q '.Output ini terus mencerminkan keadaan semasa dan sebaliknya, yang membolehkan litar menyesuaikan dan bertindak balas terhadap perubahan input masa nyata.

Flip-flop JK beroperasi dengan cara tertentu berdasarkan nilai input:

• Apabila kedua -dua J dan K adalah 0: Flip-flop memegang keadaan semasa.Tiada perubahan berlaku.

• Apabila kedua -dua J dan K adalah 1: Flip-flop bertukar keadaannya.Jika Q adalah 0, ia menjadi 1;Jika Q adalah 1, ia beralih ke 0. Tindakan togol ini adalah ciri utama yang membezakan jk flop-flop dari reka bentuk yang lebih mudah.

• Bila J adalah 1 dan k ialah 0: Flip-flop menetapkan keadaannya, menjadikan Q sama dengan 1.

• Bila J adalah 0 dan k ialah 1: Reset flip-flop, menjadikan Q sama dengan 0.

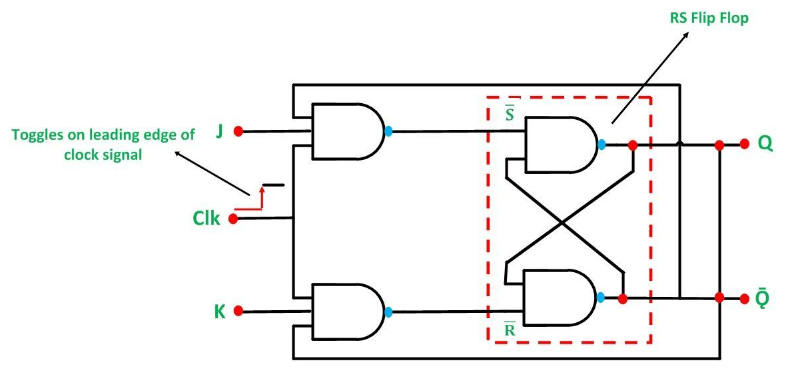

Operasi Flip-Flop JK

Flip-flop JK memainkan peranan penting dalam litar digital dengan menguruskan memori dan masa melalui tindak balas yang diselaraskan kepada isyarat input dan denyutan jam.Operasinya sangat bergantung pada masa input J dan K berbanding dengan isyarat jam, yang menentukan bagaimana output menyatakan (Q dan Q̅) berubah.Penyegerakan ini memastikan bahawa flip-flop berkelakuan boleh diramalkan dalam pelbagai aplikasi litar.Flip-flop bergantung kepada NAND atau NOR GATES untuk menguruskan perubahan keadaan ini.

Memegang keadaan semasa- Apabila kedua-dua input J dan K adalah rendah (0), flip-flop menyimpan keadaan semasa.Pintu logik dengan berkesan "mengunci" output, memastikan keadaan sebelumnya (sama ada tinggi atau rendah) dikekalkan.Fungsi pegangan ini serius dalam aplikasi di mana data mesti kekal stabil sehingga perubahan tertentu adalah suatu keharusan.

Menetapkan output tinggi (set keadaan) -Apabila nadi jam berlaku dan j adalah tinggi (1) manakala k tetap rendah (0), pintu logik menyesuaikan diri untuk menetapkan flip-flop.Ini mendorong output Q ke keadaan yang tinggi (1).Ini berguna dalam situasi di mana litar perlu mencetuskan output yang tinggi, sebagai contoh, mengaktifkan peranti atau menyimpan "1" dalam ingatan.

Membersihkan output rendah (tetapkan semula keadaan) - Jika j adalah rendah (0) dan k adalah tinggi (1) pada masa nadi jam, peralihan flip-flop ke keadaan semula, memaksa Q untuk menjadi rendah (0).Tindakan penetapan ini sering digunakan dalam litar yang memerlukan keadaan lalai atau dibersihkan selepas menyelesaikan operasi, seperti membersihkan data dari ingatan.

Toggling output - Ciri unik Flip-Flop muncul apabila kedua-dua J dan K adalah tinggi (1).Apabila denyut jam tiba, flip-flop bertukar-tukar, menukar output dari keadaan semasa ke yang bertentangan.Jika Q adalah tinggi, ia menjadi rendah, dan jika Q adalah rendah, ia menjadi tinggi.Fungsi togol ini bersungguh -sungguh dalam aplikasi seperti kaunter atau peranti yang perlu bergantian antara negeri secara automatik.

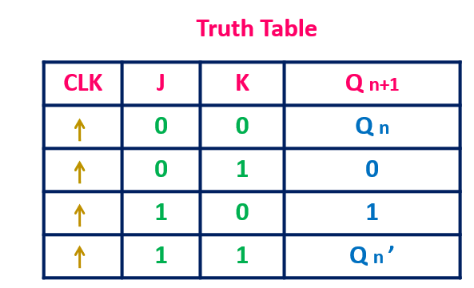

Rajah 2: Jadual kebenaran flip-flop JK

Analisis meja kebenaran jk flip-flop

Jadual kebenaran jk flop-flop adalah alat utama untuk menggambarkan bagaimana ia bertindak balas terhadap isyarat input yang berlainan selaras dengan denyutan jam.Jadual ini membantu dalam merancang dan menyelesaikan masalah litar digital dengan menunjukkan bagaimana output flip-flop berubah berdasarkan pelbagai keadaan input.

• Kedua -dua J dan K rendah (j = 0, k = 0): Apabila kedua-dua input adalah 0, flip-flop memegang keadaan semasa.Sama ada Q adalah tinggi atau rendah, ia tetap tidak berubah.Ini perlu diperhatikan untuk litar di mana pengekalan data yang stabil dikehendaki, seperti unsur-unsur memori, di mana memelihara keadaan semasa sesuai sehingga perubahan tertentu dicetuskan.

• J tinggi, k rendah (j = 1, k = 0): Apabila j ialah 1 dan k ialah 0, flip-flop menetapkan output q hingga tinggi (1).Keadaan tetapan ini berguna dalam aplikasi yang memerlukan pencetus yang tepat untuk mengaktifkan operasi, seperti menghidupkan peranti atau memulakan urutan dalam litar logik.

• J rendah, k tinggi (j = 0, k = 1): Dengan J pada 0 dan K pada 1, flip-flop reset, menjadikan Q rendah (0).Fungsi reset ini serius dalam sistem yang perlu kembali ke keadaan lalai, seperti ketika membersihkan data atau memulakan proses.

• Kedua -dua J dan K tinggi (j = 1, k = 1): Apabila kedua-dua input adalah tinggi, flip-flop bertukar keadaannya.Jika Q adalah tinggi, ia menjadi rendah, dan jika Q adalah rendah, ia beralih ke tinggi.Tingkah laku togol ini adalah besar untuk peranti yang perlu bergantian di antara negeri -negeri, seperti dalam pembahagi kekerapan atau kaunter.

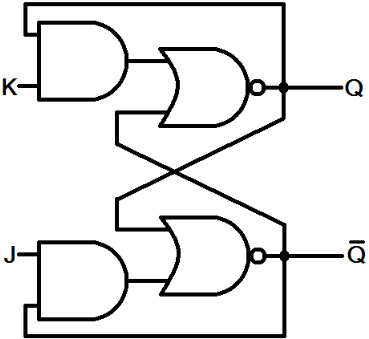

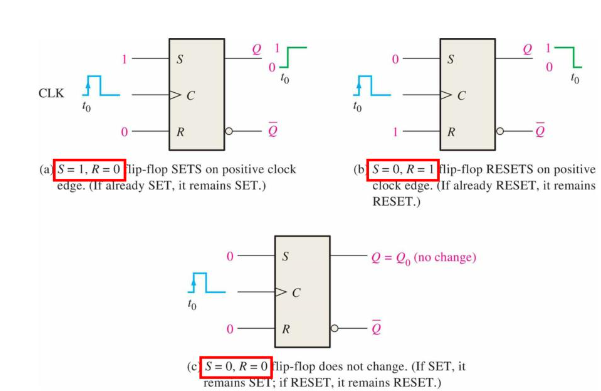

Rajah 3: JK Latch

Wawasan ke dalam operasi dan kegunaan JK Latch

Selak JK beroperasi sama dengan jk-flop JK tetapi tanpa memerlukan isyarat jam.Daripada menunggu kelebihan jam, selak JK bertindak balas secara berterusan untuk memasukkan perubahan, menjadikannya "sensitif tahap."Ini bermakna selagi input (J dan K) stabil, output akan berubah dalam masa nyata, yang menawarkan maklum balas segera berdasarkan keadaan input.

Tidak seperti flop-flop JK yang dicetuskan kelebihan, yang mengemas kini outputnya hanya apabila isyarat jam berubah (dari rendah ke tinggi atau sebaliknya), JK Latch menyesuaikan outputnya dengan serta-merta sebagai shift input.Ini responsif yang berterusan dan masa nyata adalah berharga dalam senario di mana tindakan segera dikehendaki tanpa kelewatan yang disebabkan oleh penyegerakan jam.

Penapis Kebisingan: Dalam litar digital yang perlu dengan cepat menyaring bunyi yang tidak diingini, tindak balas segera JK Latch terhadap perubahan input berpengaruh.Kerana ia tidak menunggu denyutan jam, ia boleh menyesuaikan output sebaik sahaja bunyi dikesan, mencegah kelewatan dalam pembetulan isyarat.

Elemen Memori Ringkas: Selak JK boleh berfungsi sebagai unit memori asas dalam sistem yang tidak memerlukan kawalan yang kompleks.Oleh kerana selak menyimpan output yang stabil selagi input tidak berubah, ia secara berkesan memegang keadaan semasa, yang berguna untuk litar yang perlu mengekalkan maklumat tanpa overhead operasi yang diperolehi.

Rajah 4: Analisis Gambarajah Masa untuk Flip-Flop JK

Menganalisis gambarajah masa jk-flop JK

Rajah masa jk flip-flop memberikan pecahan visual bagaimana output bertindak balas terhadap input yang berbeza, disegerakkan dengan peralihan nadi jam.Rajah ini menunjukkan hubungan antara isyarat jam (CLK) dan input (J dan K), dan bagaimana mereka secara kolektif mempengaruhi output (Q dan Q ').Ia membantu memetakan tingkah laku flip-flop di seluruh negara berurutan, menjadikannya lebih mudah untuk memahami operasinya.

Pertama, gambarajah menyoroti bahawa output dikemas kini hanya pada tepi yang semakin meningkat atau jatuh dari nadi jam.Ciri ini, yang dikenali sebagai Edge-Triggering, dominan kepada operasi JK Flip-Flop.Ia menunjukkan bahawa walaupun input J dan K berubah, output tetap tidak berubah sehingga kelebihan jam berlaku, memastikan peralihan yang boleh diramal dan stabil.

Kemudian, kerana rajah memetakan variasi input j dan k, secara visual Menunjukkan bagaimana setiap gabungan input mempengaruhi output. Sebagai contoh, apabila kedua -dua J dan K adalah rendah (0), output memegang keadaan semasa.Apabila j adalah tinggi dan k adalah rendah, output ditetapkan.Perwakilan visual yang jelas ini membantu pengguna memahami bagaimana flip-flop bertindak balas terhadap kombinasi input yang berbeza dalam masa nyata.

Akhirnya, Gambar rajah masa jelas menunjukkan peralihan antara keadaan output yang berbeza, sama ada memegang, menetapkan, menetapkan semula, atau bertukar.Setiap perubahan keadaan terikat secara langsung kepada keadaan input dan kelebihan jam, menunjukkan hubungan sebab-sebab yang fokus untuk merancang dan menyelesaikan masalah.

Aplikasi serba boleh jk-flop JK

Flip-flop JK adalah komponen teras dalam pelbagai sistem digital, yang terkenal dengan fleksibiliti dan kebolehpercayaan mereka.Keupayaan mereka untuk mengendalikan operasi logik kompleks menjadikan mereka diperlukan dalam beberapa aplikasi utama, termasuk:

Rajah 5: Penyimpanan Memori

JK flip-flop biasanya digunakan untuk menyimpan bit individu data, menjadikannya elemen asas dalam tatasusunan memori dan daftar.Setiap flip-flop memegang sedikit, memastikan penyimpanan data yang boleh dipercayai, yang bermanfaat dalam reka bentuk sistem memori yang lebih besar.

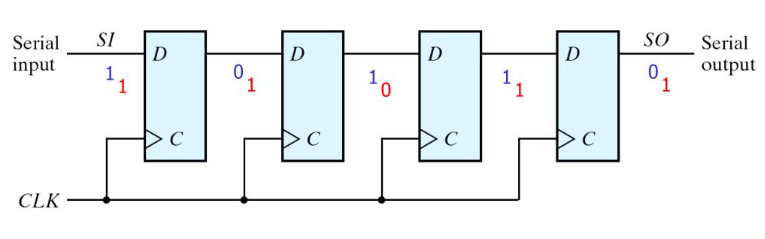

Rajah 6: Kaunter dan daftar peralihan

JK flip-flop adalah dinamik dalam operasi penjujukan.Mereka digunakan secara meluas dalam kaunter untuk mengira peristiwa atau denyutan dan dalam daftar peralihan untuk menukar data siri ke dalam format selari.Ini menjadikan mereka berguna dalam mengurus dan memanipulasi data di pelbagai peringkat proses, seperti dalam sistem komunikasi.

Rajah 7: Bahagian Kekerapan

Dalam pemprosesan isyarat, jk-flop JK sering digunakan untuk pembahagian kekerapan.Dengan menukarkan keadaan mereka dengan setiap nadi jam, mereka membahagikan kekerapan isyarat input, mewujudkan isyarat jam yang lebih perlahan dan lebih mudah diuruskan.Ini perlu diberi perhatian dalam aplikasi seperti Pengurusan Isyarat Jam, di mana kawalan masa dikehendaki.

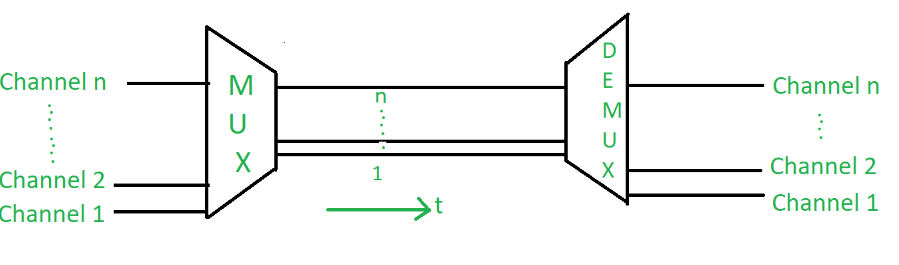

Rajah 8: Penyegerakan

JK flip-flop membantu menyegerakkan pelbagai proses digital dengan memastikan bahawa bahagian-bahagian sistem yang berlainan beroperasi bersama-sama dengan cara yang diselaraskan.Mereka memastikan bahawa pelbagai komponen bertindak balas dengan betul kepada isyarat masa, menjaga seluruh sistem disegerakkan.

Rajah 9: JK Flip-Flop: EDGE-dicetuskan dan dicetuskan tahap

Pelbagai jenis flip jk

Flip-flop JK boleh didapati dalam dua jenis utama: kelebihan yang dicetuskan dan dicetuskan tahap, masing-masing direka untuk keperluan operasi yang berbeza.

JK flip-flop yang dicetuskan tepi: Tukar keadaan mereka hanya pada titik tertentu -apabila peralihan isyarat jam dari rendah ke tinggi (naik pinggir) atau tinggi ke rendah (jatuh).Ciri ini menjadikan mereka sesuai untuk sistem di mana masa yang tepat adalah bersungguh -sungguh.Kerana perubahan keadaan berlaku tepat pada tepi jam, flip-flop ini memastikan semua kemas kini berlaku selaras dengan nadi jam.Tingkah laku yang boleh diramal ini dinamik dalam persekitaran yang dikawal ketat seperti jam digital, daftar, dan litar yang paling berurutan.Di sini, masa setiap perubahan adalah serius untuk mengekalkan kestabilan sistem dan memastikan operasi disegerakkan.

JK flip-flops yang dicetuskan tahap: Beroperasi secara berbeza, bertindak balas terhadap isyarat input selagi isyarat jam berada pada tahap tertentu -sama ada tinggi atau rendah.Mereka tidak menunggu peralihan jam tertentu.Sebaliknya, selagi input memenuhi syarat yang diperlukan, flip-flop akan mengubah keadaan.Tingkah laku ini menjadikan flip-flop yang dicetuskan tahap lebih sesuai untuk sistem asynchronous, di mana input mungkin tidak sejajar dengan nadi jam biasa.Mereka menyediakan fleksibiliti dalam sistem di mana input tidak dapat diramalkan atau tiba pada selang yang tidak teratur, seperti dalam tugas pemprosesan isyarat tertentu atau sistem pemantauan yang mesti bertindak balas dengan segera kepada perubahan input.

Kelebihan dan keburukan jk flop

JK flip-flop menawarkan beberapa faedah tetapi juga datang dengan beberapa perdagangan yang perlu ditimbang dengan teliti ketika merancang sistem digital.

|

Kelebihan |

|

|

Fleksibiliti |

Jk flip-flop sangat fleksibel dan boleh

digunakan dalam pelbagai litar digital seperti penyimpanan memori, kaunter, dan

sistem kawalan.Mereka boleh bertukar, menetapkan, atau menetapkan semula berdasarkan input yang berbeza

syarat, menjadikannya sesuai untuk pelbagai aplikasi yang

memerlukan kawalan yang tepat terhadap peralihan negeri. |

|

Mekanisme pembetulan diri |

Salah satu ciri yang menonjol JK

Flip-flop adalah gelung maklum balas terbina dalam, yang membantu logik yang betul

menyatakan secara dinamik.Pembetulan diri ini memastikan litar kekal

Stabil semasa operasi, walaupun input berubah dengan cepat. |

|

Pengurangan keadaan kaum |

Tidak seperti flip-flop yang lebih mudah, jk-flop JK

direka untuk mencegah keadaan perlumbaan -situasi di mana output menjadi

tidak stabil kerana isyarat input yang bertentangan.Keupayaan ini untuk mengekalkan

output yang konsisten, walaupun di bawah perubahan input cepat dan berurutan, meningkatkan

Kebolehpercayaan litar. |

|

Keburukan |

|

|

Reka bentuk kompleks |

Jk flip-flop lebih rumit daripada

Flip-flops asas.Reka bentuk mereka memerlukan pintu logik tambahan dan input

pemantauan, yang boleh menjadikan litar lebih sukar untuk mereka bentuk dan

menyelesaikan masalah, terutamanya dalam sistem di mana kesederhanaan lebih disukai. |

|

Kelewatan penyebaran |

Gating dalaman digunakan untuk menguruskan keadaan

Peralihan memperkenalkan kelewatan seberapa cepat isyarat dapat diproses.Dalam

Aplikasi berkelajuan tinggi, kelewatan ini boleh menjejaskan masa keseluruhan dan melambatkan

prestasi litar. |

|

Penggunaan kuasa yang lebih tinggi |

Kerana kerumitan mereka dan keperluan untuk

Sentiasa memantau keadaan input, jk-flop JK menggunakan lebih banyak kuasa

berbanding dengan flip-flop yang lebih mudah.Dalam sistem yang lebih besar atau sensitif kuasa

aplikasi, permintaan kuasa yang lebih tinggi ini boleh menjadi kelemahan |

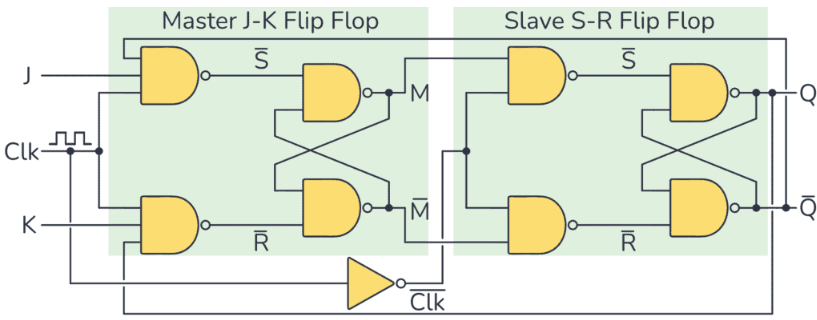

Rajah 10: Flip-Flop JK Master-Slave

Menyahkod flip-flop jk master-hamba

Flip-flop JK Master-hamba direka untuk menyelesaikan keadaan kaum yang terdapat dalam flip-flop JK standard dengan menggunakan proses dua langkah untuk menguruskan input dan output dengan lebih cekap.

Tahap pertama, yang dipanggil Tahap Master, menangkap nilai input apabila isyarat jam mencapai kelebihan tertentu, sama ada meningkat atau jatuh.Pada ketika ini, data input dikunci, yang bermaksud bahawa perubahan selanjutnya kepada input tidak menjejaskan keadaan yang ditangkap sehingga kitaran jam seterusnya.Tahap ini memastikan bahawa flip-flop mendaftarkan input yang betul tanpa dipengaruhi oleh sebarang perubahan berikutnya semasa kitaran jam yang sama.

Selepas peringkat tuan selesai, peringkat hamba dimainkan.Tahap ini mengemas kini output berdasarkan data yang ditangkap oleh peringkat induk, tetapi hanya pada kelebihan jam seterusnya.Dengan memisahkan penangkapan input dari kemas kini output, peringkat hamba memastikan bahawa output tetap stabil sehingga tahap induk telah memproses input sepenuhnya.Ini menghalang sebarang perubahan pramatang atau tidak diingini dalam output semasa kitaran jam.

Mengapa konfigurasi tuan-hamba penting?

Proses dua peringkat menstabilkan operasi flip-flop JK, menghalang ayunan atau turun naik yang tidak diingini yang boleh berlaku dalam konfigurasi yang lebih mudah, terutamanya apabila kedua-dua input dipegang tinggi.Dengan decoupling pemprosesan input dari perubahan output, konfigurasi master-hamba memastikan bahawa output tetap diramal dan stabil, walaupun dalam situasi di mana masa adalah berharga.

Menangani perlumbaan di sekitar keadaan di jk-flop

Keadaan perlumbaan berlaku di jk-flop JK apabila kedua-dua input, J dan K, tinggi, dan isyarat jam tetap aktif terlalu lama.Ini membawa kepada penalaan berterusan output, yang boleh menyebabkan tingkah laku yang tidak menentu dan mengganggu kebolehpercayaan litar.

Persediaan master-hamba menggunakan proses dua peringkat untuk mencegah isu-isu kaum.Tahap induk menangkap nilai input di tepi jam dan mengunci mereka. Tahap hamba mengemas kini output pada tepi jam seterusnya, memastikan output tidak berubah sehingga input diproses sepenuhnya.Pendekatan ini secara berkesan menghalang output daripada bertukar -tukar tanpa kawalan, walaupun input kekal tinggi untuk tempoh yang panjang.

Kaedah lain untuk mengelakkan keadaan kaum adalah menyesuaikan tempoh nadi jam.Dengan membuat denyut jam lebih pendek daripada kelewatan penyebaran flip-flop, anda dapat memastikan bahawa negara tidak berubah lebih dari sekali dalam kitaran jam yang sama.Ini menghalang flip-flop dari bertukar berulang kali semasa satu kitaran, menstabilkan output.

Dinamik Beralih di JK Flip-Flops

Tingkah laku beralih flip-flop JK sebahagian besarnya didorong oleh masa isyarat jam dan tahap input (J dan K).Perubahan flip-flop keadaan berdasarkan input yang terdapat pada tepi positif isyarat jam.Pada masa yang berbahaya ini, flip-flop menilai input dan mengemas kini outputnya dengan sewajarnya.

Apabila isyarat jam mencecah kelebihan yang semakin meningkat, jk-flop JK membaca keadaan semasa input J dan K.Bergantung pada nilai mereka, flip-flop sama ada memegang, menetapkan, menetapkan semula, atau bertukar outputnya.

Jam digital: Ketepatan adalah segala-galanya dalam jam digital, dan jk flop-flop membantu mengekalkan ketepatan ini dengan memastikan perubahan keadaan hanya berlaku pada selang waktu yang tepat.

Penguji logik berurutan: Dalam sistem yang menguji fungsi litar logik, jk flip-flop memainkan peranan dalam mengesahkan bahawa setiap komponen bertindak balas dengan betul kepada isyarat masa tertentu.

Sistem sensitif masa lain: Dalam pelbagai aplikasi digital di mana masa berisiko, seperti sistem komunikasi atau unit pemprosesan data, jk flop-flop memastikan bahawa peralihan negara berlaku selaras dengan jam, menghalang kesilapan masa.

Kesimpulan

Flip-flop JK menonjol sebagai elemen utama dalam reka bentuk litar digital, yang menawarkan perpaduan fleksibiliti dan ketepatan yang terdesak untuk pelbagai aplikasi yang terdiri daripada penyimpanan memori ke bahagian kekerapan dan penyegerakan proses digital.Keupayaannya untuk mengurangkan keadaan kaum melalui konfigurasi inovatif seperti susunan tuan-hamba yang menggariskan kesesuaiannya dalam menyelesaikan cabaran reka bentuk yang wujud.Begitu juga, peranan kubur flip-flop dalam memastikan peralihan keadaan yang tepat menyoroti sifatnya yang diperlukan dalam penciptaan dan penyelenggaraan sistem digital yang boleh dipercayai dan cekap.Sebagai kemajuan teknologi, reka bentuk dan aplikasi yang berkembang dari flip-flop JK terus menjadi kunci dalam menolak sempadan elektronik digital ke arah seni bina yang lebih canggih dan mantap.

Soalan Lazim [Soalan Lazim]

1. Apakah aplikasi JK Flip Flop?

Flip-flop JK digunakan secara meluas dalam elektronik digital untuk pelbagai tugas:

Aplikasi masa: Ia boleh berfungsi sebagai elemen kelewatan atau pemasa apabila disambungkan dalam konfigurasi tertentu.

Kaunter dan daftar: Dengan menukarkan keadaannya dengan setiap nadi jam, ia digunakan dalam merancang pelbagai kaunter dan daftar peralihan yang paling utama dalam litar logik berurutan.

Penyimpanan Memori: Ia menyediakan unit asas penyimpanan memori, berguna dalam menyimpan bit dalam aplikasi pengiraan.

2. Bagaimanakah jk flop-flop berfungsi dengan jadual kebenaran?

JK Flip-Flop mempunyai dua input (J dan K) dan isyarat jam.Operasinya berbeza berdasarkan keadaan input, disegerakkan pada jam:

• J = 0, k = 0: Output tidak berubah.

• j = 0, k = 1: output ditetapkan semula ke 0.

• J = 1, k = 0: Output ditetapkan kepada 1.

• J = 1, k = 1: output bertukar (iaitu, jika 0, ia menjadi 1 dan sebaliknya).

3. Apakah JK Flip Flop dan adakah ia berfungsi?

A JK Flip-Flop menggabungkan sifat-sifat Sr dan T flop-flop.Ia menghindari keadaan "dilarang" yang dilihat dalam flip-flop SR dengan menggunakan input JK dengan berkesan:

Keadaan flip-flop dikawal oleh input j dan k, yang menentukan sama ada output harus memegang, menetapkan semula, menetapkan, atau bertukar-tukar, selaras dengan kenaikan atau kelebihan pulse jam.

4. Apakah aplikasi selak dan flip-flop?

Penyimpanan Data: Selak dan flip-flop serius untuk penyimpanan data dalam daftar dan tatasusunan memori.

Bahagian Kekerapan: Digunakan dalam pembahagi frekuensi kerana keupayaan mereka untuk menukar negeri pada tepi jam, mengurangkan kekerapan dengan setiap peringkat dalam siri.

Mesin Negeri: Asas dalam merancang mesin negeri terhingga yang digunakan untuk melaksanakan litar logik dan kawalan berurutan.

Debouncing: Digunakan untuk menstabilkan isyarat dari suis dan butang mekanikal, memastikan peralihan tunggal dan bersih.

5. Apakah flip-flop yang digunakan?

Penyimpanan Perduaan: Setiap flip-flop menyimpan satu data, menjadikannya blok bangunan untuk peranti penyimpanan binari.

Pembahagi Jam: Mereka membahagikan kekerapan jam input dengan dua, berguna dalam jam digital dan aplikasi masa.