RumahBlogPanduan terperinci untuk penambah penuh

Panduan terperinci untuk penambah penuh

Dalam bidang elektronik digital dan kejuruteraan komputer, penambah mewakili salah satu blok bangunan yang paling penting, penting dalam pembinaan dan fungsi litar aritmetik yang lebih rumit.Sebagai komponen integral unit logik aritmetik (ALU), penambah memudahkan operasi pengkomputeran yang banyak, dari aritmetik asas kepada tugas logik kompleks yang diperlukan untuk operasi sistem.Reka bentuk mereka, yang boleh berbeza-beza dari setengah tambahan kepada penambah penuh yang lebih kompleks, memainkan peranan penting dalam meningkatkan kecekapan dan kelajuan pemprosesan dalam sistem digital.Artikel ini menyelidiki seni bina terperinci dan nuansa fungsional pelbagai jenis penambah, yang menggambarkan peranan kritikal mereka dalam teknologi pengkomputeran moden dan meneroka logik, litar, dan aplikasi operasi mereka dalam konteks reka bentuk logik digital yang lebih luas.

Katalog

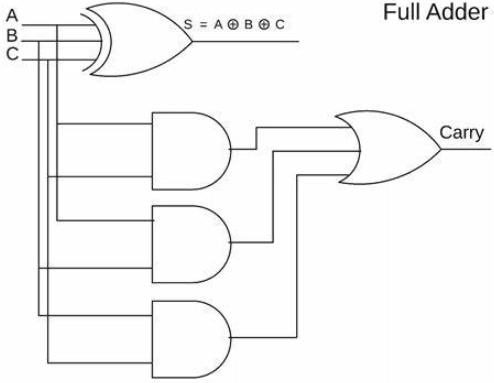

Rajah 1: Penambah penuh

Penambah adalah komponen asas dalam kejuruteraan elektronik dan reka bentuk logik digital dan memainkan peranan utama dalam sistem komputer yang lebih kompleks.Sebagai sebahagian daripada Unit Logik Aritmetik (ALU), penambah mengendalikan pelbagai tugas pengkomputeran penting.Kecekapan dan prestasi keseluruhan pemproses secara langsung dipengaruhi oleh reka bentuk dan fungsi penambah.

Dalam pemproses, penambah digunakan bukan hanya untuk operasi aritmetik asas seperti tambahan dan penolakan, tetapi ia juga terlibat dalam pelbagai operasi logik yang lebih luas.Sebagai contoh, apabila menjalankan program, pemproses sering perlu mengira alamat memori baru.Ini biasanya dilakukan dengan menambah atau menolak dari alamat semasa -tugas yang dilakukan oleh penambah.Mereka mengawal bilangan lelaran gelung dan aliran keseluruhan dengan meningkatkan dan menurunkan kaunter.Dalam aplikasi yang lebih kompleks, seperti pengindeksan jadual, penambah dengan cepat mencari data dengan mengira offset.Ini penting untuk sistem pengurusan pangkalan data, pembinaan pengkompil, dan pemprosesan data berskala besar.Adders juga penting dalam melaksanakan teknik pemetaan tertentu dalam sistem cache pelbagai peringkat, menggunakan operasi aritmetik untuk menentukan kedudukan data dalam cache, sehingga mengoptimumkan kecekapan akses.

Secara teknologi, penambah dilaksanakan melalui pelbagai reka bentuk litar termasuk penambah selari, siri, dan saluran paip.Penambah selari disukai kerana keupayaan mereka untuk mengendalikan pelbagai digit secara serentak, menjadikannya sesuai untuk senario yang memerlukan pengiraan pantas.Penambah siri, sebaliknya, memproses sedikit setiap kitaran jam dan sesuai untuk persekitaran yang terhad atau rendah.Penambah saluran paip membahagikan proses tambahan ke beberapa peringkat, masing -masing mengendalikan sebahagian daripada operasi tambahan.Reka bentuk ini meningkatkan kelajuan pengiraan, terutamanya dalam persekitaran pengkomputeran berprestasi tinggi.

Litar separuh tambahan adalah blok bangunan asas dalam elektronik digital, yang direka khusus untuk menambah dua digit binari tunggal.Litar ini membentuk asas penambah penuh dan merupakan kunci untuk memahami reka bentuk litar logik yang lebih kompleks.Dalam setengah penambah, terdapat dua input utama, dilabelkan A dan B, yang mewakili Augend dan Addend masing -masing.Persediaan ini membolehkannya mengira jumlah dan membawa output tanpa memerlukan input membawa dari pengiraan sebelumnya.

Inti dari setengah tambahan terdiri daripada dua pintu logik: pintu XOR dan pintu dan pintu.Pintu XOR bertanggungjawab untuk menghasilkan output jumlah.Ia beroperasi di bawah peraturan mudah di mana ia mengeluarkan 1 jika hanya satu daripada inputnya adalah 1;Jika tidak, ia mengeluarkan 0. dan pintu, di sisi lain, mengendalikan output bawa.Ia menghasilkan 1 hanya apabila kedua -dua inputnya adalah 1, menjajarkan dengan sempurna dengan keperluan asas tambahan binari.

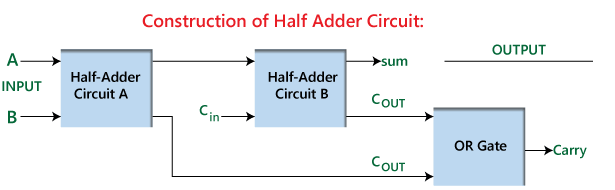

Rajah 2: Pembinaan separuh penambah

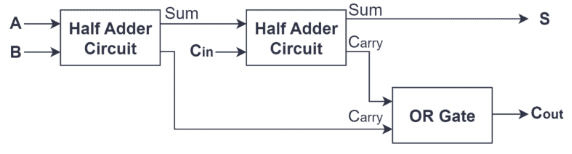

Reka bentuk yang cekap dan mudah ini membolehkan separuh penambah bukan sahaja untuk melakukan penambahan binari asas secara bebas tetapi juga untuk berfungsi sebagai blok bangunan untuk mewujudkan penambah penuh.Penambah penuh dibina dengan menggabungkan dua setengah penambah dengan pintu tambahan atau pintu.Dalam persediaan ini, penambah separuh pertama mengambil tugas tambahan awal, menghasilkan jumlah awal dan dibawa.Separuh kedua Adder kemudian memproses bawa dari yang pertama bersama -sama dengan input membawa tambahan.Akhirnya, pintu OR menggabungkan dua output membawa untuk menghasilkan output bawa akhir.Susunan ini meningkatkan fungsi penambah, membolehkannya mengendalikan tugas tambahan multi-bit yang lebih kompleks, mempamerkan aplikasi yang meluas dan kepentingan setengah penambah dalam reka bentuk litar digital.

Penambah penuh adalah komponen canggih dalam reka bentuk logik digital, dilengkapi untuk mengendalikan penambahan tiga input binari tunggal, yang biasanya dilabelkan sebagai A, B, dan Carry-In (CIN).Reka bentuk ini membolehkan penambah penuh untuk memproses penambahan binari kompleks dengan cekap dengan memasukkan bawa dari pengiraan pesanan rendah sebelumnya ke dalam satu operasi.

Rajah 3: Litar penambah penuh

Secara fungsional, penambah penuh boleh mengeluarkan jumlah dua angka, yang bermaksud outputnya boleh berkisar dari 0 hingga 3, dan ia juga boleh menghasilkan pembawa (cout).Ini berlaku kerana, apabila semua bit input ditetapkan kepada 1 (a = 1, b = 1, cin = 1), output jumlah akan menjadi 1 (mewakili binari 01), dan pembawa keluar 1 dihasilkan, menunjukkan bahawaPembawa tambahan perlu diluluskan kepada bit yang lebih tinggi seterusnya.

Secara struktural, penambah penuh umumnya terdiri daripada dua setengah penambah dan satu atau pintu.Penambah separuh pertama mengambil input A dan B, menghasilkan jumlah awal dan isyarat bawa.Jumlah awal ini kemudian diberi makan, bersama dengan pembawa (CIN), ke dalam separuh kedua.Peranan penambah separuh kedua adalah untuk menambah jumlah ini dari separuh masa pertama ke CIN, menghasilkan jumlah lain dan output bawa baru.Pada masa yang sama, output membawa dari separuh pertama penambah dan output bawa dari separuh kedua penambah digabungkan melalui pintu atau pintu, memuncak dalam pembawa terakhir (cout) penambah penuh.Reka bentuk struktur ini memastikan bahawa penambah penuh secara berkesan mengendalikan penyebaran pembawa sebagai tambahan, menjadikannya sesuai untuk melaksanakan penambahan binari multi-bit.Oleh itu, reka bentuk penambah penuh bukan sahaja mempercepatkan pemprosesan data dan meningkatkan kecekapan tetapi juga memudahkan kerumitan pelaksanaan perkakasan melalui kombinasi logik yang mudah, menjadikannya komponen yang sangat diperlukan dalam penambahan multi-angka dan unit logik aritmetik (Alu (Alu).

|

Parameter

|

Separuh penambah

|

Penambah penuh

|

|

Penerangan

|

Half Adder adalah logik gabungan

Litar yang menambah dua digit 1-bit.Tingkat separuh menghasilkan sejumlah kedua-dua

input.

|

Penambah penuh adalah logik gabungan

Litar yang melakukan operasi tambahan pada tiga nombor binari satu-bit.

Penambah penuh menghasilkan sejumlah tiga input dan nilai bawa.

|

|

Membawa sebelumnya

|

Pembawa sebelumnya tidak digunakan.

|

Pembawa sebelumnya digunakan.

|

|

Input

|

Pada separuh penambah, terdapat dua bit input (a,

B).

|

Secara penuh, terdapat tiga bit input

(A, b, cdalam).

|

|

Output

|

Output yang dihasilkan adalah dua bit-jumlah

dan bawa dari input 2 bit.

|

Output yang dihasilkan adalah dua bit-jumlah

dan bawa dari input 3 bit.

|

|

Digunakan sebagai

|

Litar setengah penambah tidak boleh digunakan

cara yang sama seperti litar penambah penuh.

|

Litar penambah penuh boleh digunakan di tempatnya

daripada separuh litar penambah.

|

|

Ciri

|

Ia mudah dan mudah dilaksanakan

|

Reka bentuk penambah penuh tidak seperti

Mudah sebagai setengah penambah.

|

|

Ungkapan logik

|

Ekspresi logik untuk setengah penambah adalah:

S = a⊕b;C = a*b.

|

Ekspresi logik untuk penambah penuh adalah:

S = a⊕b⊕cin;Ckeluar= (a*b)+(cdalam*(a⊕b)).

|

|

Pintu logik

|

Ia terdiri daripada satu pintu gerbang dan satu dan

pintu gerbang.

|

Ia terdiri daripada dua bekas atau dua dan pintu,

dan satu atau pintu.

|

|

Aplikasi

|

Ia digunakan dalam kalkulator, komputer,

Peranti pengukur digital, dll.

|

Ia digunakan dalam penambahan bit berbilang,

pemproses digital, dll.

|

|

Nama lain

|

Tidak ada nama alternatif selama separuh

penambah.

|

Penambah penuh juga dikenali sebagai pembawa riak

penambah.

|

Carta

1: Perbezaan antara penambah separuh dan penambah penuh

Jadual kebenaran penambah penuh adalah kunci untuk memahami logik operasinya, yang memperincikan hubungan yang tepat antara kombinasi input binari dan output yang sepadan.Jadual ini menunjukkan semua senario input yang berpotensi dan hasilnya, menjadikannya alat penting dalam reka bentuk dan pengesahan litar logik digital.Penambah penuh memproses tiga input: A, B, dan A Carry-In (CIN), masing-masing boleh sama ada 0 atau 1. Ini menghasilkan lapan kemungkinan kombinasi input.

Bagi setiap kombinasi ini, output dari penambah penuh termasuk jumlah (jumlah) dan pembawa (cout).Jumlahnya adalah penambahan modulo-2 (operasi XOR) daripada tiga input-A, B, dan CIN.Pembawa berlaku apabila sekurang-kurangnya dua bit input adalah 1. Ini mencerminkan keupayaan penambah penuh untuk mengendalikan operasi tambahan dalam operasi penambahan, memastikan ketepatan dalam pengiraan yang lebih tinggi.

Untuk menggambarkan, pertimbangkan senario input di mana semua input adalah 0 (a = 0, b = 0, c-in = 0).Jumlah output akan menjadi 0, dan bawa juga akan menjadi 0, menunjukkan bahawa tidak ada jumlah tambahan atau dibawa untuk mengurus.Jika hanya satu bit input adalah 1, seperti A = 1, B = 0, C-in = 0, jumlah output akan menjadi 1 tanpa dibawa, menunjukkan bahawa tidak perlu memindahkan bawa ke bit yang lebih tinggi.Apabila dua bit input adalah 1, seperti a = 1, b = 1, c-in = 0, jumlah output adalah 0 (sejak 1+1 sama dengan 2 dalam binari, dan modulo-2 hasil dalam 0), tetapi bawa-Keluar adalah 1, menunjukkan bawa yang perlu diserahkan kepada bit yang lebih tinggi seterusnya.Senario yang paling kompleks berlaku apabila ketiga-tiga bit input adalah 1 (a = 1, b = 1, c-in = 1);Jumlah output adalah 1, dan terdapat pembawa keluar 1, menunjukkan bahawa pengurusan membawa juga diperlukan pada bit yang lebih tinggi.

|

A

|

B

|

Cdalam

|

S

|

Ckeluar

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

Carta 2: Jadual Kebenaran Penambah Penuh

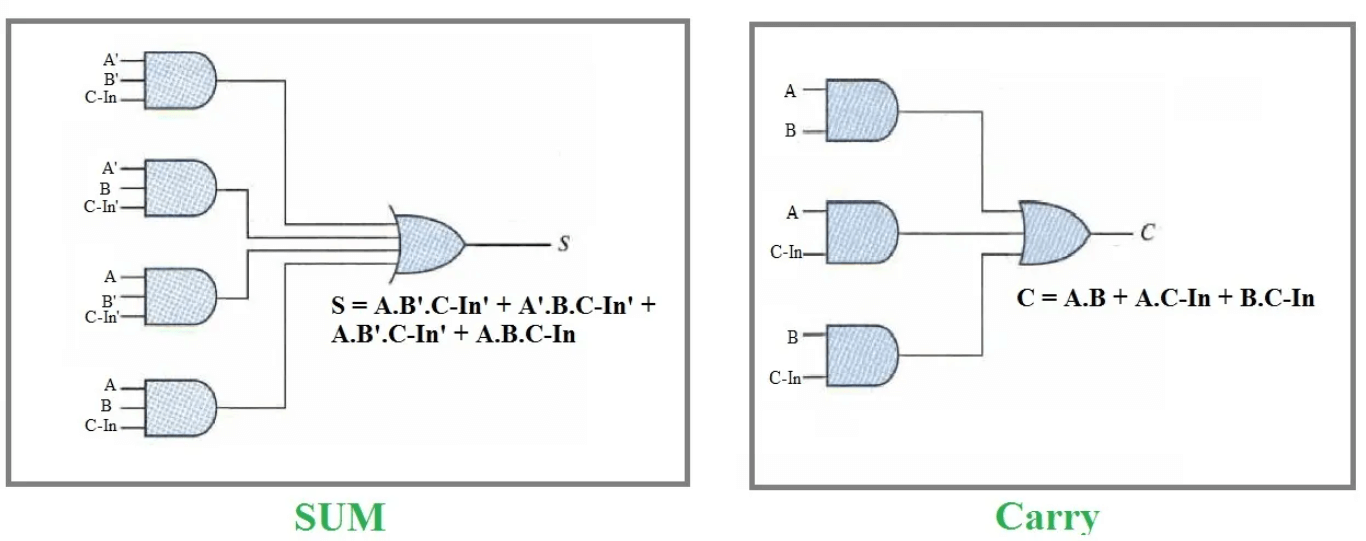

Memahami penambah penuh melibatkan membedah fungsinya menggunakan jadual kebenaran, di mana kombinasi nilai input yang berbeza A, B, dan C-in membawa kepada output jumlah dan cout.Untuk memahami operasi, kami memudahkan persamaan logik langkah demi langkah.

Ungkapan logik untuk jumlah

Persamaan bermula dengan kes -kes yang berbeza di mana jumlahnya sama dengan 1:

• A 'b' cin + a 'b cin' + a b 'cin' + ab cin

Persamaan ini boleh dipendekkan dengan mengumpulkan istilah dengan dan tanpa CIN:

• cin (a 'b' + ab) + cin '(a' b + a b ')

Penyederhanaan ini membawa kepada bentuk yang lebih mudah untuk dilaksanakan:

• CIN XOR (A XOR B)

Perwakilan ini menunjukkan bahawa output jumlahnya pada dasarnya adalah operasi XOR di antara A, B, dan CIN, menangkap tingkah laku teras tambahan binari di mana jumlah togol berdasarkan bilangan yang ganjil.

Logik untuk cout

Bermula dengan syarat -syarat di mana bawaan dijana:

• A 'b cin + a b' cin + ab c-in ' + ab cin

Memudahkan persamaan, kami mengenal pasti istilah yang biasanya melibatkan menjana bawa:

• ab + b cin + a cin

Mencari kaedah lain untuk melaksanakan cout, persamaan boleh dianjurkan semula:

• ab + a cin + b c-in (a + a ')

Ini memperluaskan dan mengimbangi untuk menangkap semua senario di mana sekurang -kurangnya dua input adalah 1:

• ab cin + ab + a c-in + a 'b cin

• AB (1 + CIN) + A C-in + A 'B Cin

• ab + a c-in (b + b ') + a' b cin

• AB + A B 'CIN + A' B CIN

• AB + CIN (A 'B + A B')

Borang padat terakhir untuk cout:

• AB + CIN (A XOR B)

Versi persamaan pembawa ini menunjukkan bagaimana cout dihasilkan sama ada apabila kedua-dua A dan B adalah 1, atau apabila salah satu daripada A atau B adalah 1 bersama dengan pembawa, dengan itu merangkumi logik yang diperlukan untuk menguruskan penyebaran membawa dalam pelbagaiBit binari tambahan.Logik yang diselaraskan ini amat berguna untuk melaksanakan litar digital yang cekap.

Rajah 4: Persamaan penambah penuh

Melaksanakan litar penambah penuh melibatkan dengan berhati-hati memasang dua setengah penambah dan pintu atau pintu untuk membuat peranti yang mampu mengendalikan penambahan tiga input binari tunggal-bit.Susunan ini mengoptimumkan kerumitan litar dan memastikan pengiraan yang cekap dan tepat.

Untuk memulakan, penambah separuh pertama mengambil dua input binari utama, A dan B, yang merupakan digit utama yang akan ditambah.Tugas utamanya adalah untuk mengira jumlah dan bawa awal kedua -dua nombor ini.Di sini, separuh pertama Adder menyampaikan dua hasil: jumlah awal (SUM1) dan pembawa awal (carry1).SUM1 berasal dari operasi XOR A dan B, menunjukkan sama ada jumlahnya mempunyai bilangan ganjil 1.Carry1, hasil dan operasi antara a dan b, menunjukkan sama ada kedua -dua digit adalah 1, yang memerlukan dibawa ke bit yang lebih tinggi seterusnya.

Seterusnya, separuh kedua Adder menyertai proses itu.Ia menggunakan jumlah output SUM1 dan input ketiga CIN (dibawa dari pengiraan sebelumnya) sebagai inputnya.Penambah separuh kedua menghasilkan dua output: hasil terakhir (SUM2) dan pembawa sekunder (carry2).SUM2, yang merupakan hasil XOR dari SUM1 dan CIN, mewakili jumlah akhir tiga input, memaparkan penambahan binari agregat.Carry2, muncul dari dan operasi antara SUM1 dan CIN, menunjukkan bawaan yang dihasilkan oleh komponen ini.

Rajah 5: Litar penambah penuh dengan menggunakan dua setengah penambah

Akhirnya, untuk melengkapkan reka bentuk penambah penuh, pintu atau pintu diperlukan untuk mengendalikan output membawa1 dan membawa2 dari kedua -dua setengah penambah.Ini atau Gate memastikan bahawa sebarang bawa yang dihasilkan semasa perhitungan diteruskan dengan betul ke output akhir.Oleh itu, output bawaan akhir penambah penuh (cOUT) adalah atau hasil carry1 dan carry2.Kemasukan gerbang ini atau menjamin bahawa semua potensi yang dibawa dikira dengan tepat dan disampaikan ke peringkat seterusnya dalam operasi tambahan multi-bit, memastikan integriti operasi aritmetik merentasi pelbagai bit.

Penambah penuh memainkan peranan yang sangat diperlukan dalam reka bentuk logik digital, yang menawarkan banyak faedah yang menjadikannya penting dalam pelbagai senario pengkomputeran dan pemprosesan data.Kelebihan utama mereka termasuk fleksibiliti yang luar biasa, kelajuan pemprosesan SWIFT, dan pengurusan bawa yang cekap.Ciri-ciri ini menjadikan penambah penuh yang sesuai untuk melaksanakan operasi aritmetik dan fungsi logik yang kompleks, terutamanya dalam aplikasi yang memerlukan penambahan berbilang bit berurutan.

Kelebihan

Fleksibiliti: Penambah penuh cemerlang dalam keupayaan mereka untuk memproses pelbagai input binari (A, B, dan CIN) secara serentak.Mereka juga boleh diperluaskan ke dalam tatasusunan penambah yang lebih besar untuk mengendalikan nombor binari yang lebih lama.Skala ini penting untuk membina unit logik aritmetik berprestasi tinggi (ALUs), yang mesti menjalankan operasi aritmetik dan logik multi-bit yang rumit.

Kelajuan: Terima kasih kepada seni bina pemprosesan selari dalaman mereka, penambah penuh dapat menyelesaikan penambahan semua input dalam satu kitaran jam sementara juga menentukan untuk membawa output.Keupayaan ini menyokong operasi tambahan yang berterusan dan sangat diperlukan untuk pemprosesan data masa nyata dalam mikropemproses moden dan peranti pengkomputeran berkelajuan tinggi.

Kekurangan

Walau bagaimanapun, penambah penuh juga menunjukkan kelemahan yang ketara:

Kerumitan dalam Reka Bentuk dan Pelaksanaan: Penambah penuh melibatkan pelbagai pintu logik dan penyebaran bawa pelbagai peringkat, menjadikan kompleks reka bentuk mereka.Kerumitan ini bukan sahaja meningkatkan kos pembuatan tetapi juga boleh memberi kesan kepada kebolehpercayaan litar.

Isu Kelewatan Penyebaran: Membawa penyebaran boleh melalui beberapa pintu logik, masing -masing menambah kelewatannya.Ini boleh mengehadkan kelajuan pengiraan keseluruhan semasa operasi berskala besar, terutamanya dalam sistem komputer yang luas dan dalam reka bentuk integrasi berskala besar (VLSI) dan pemproses berkelajuan tinggi.Kelewatan ini boleh menjadi kesesakan yang ketara dalam prestasi.

Untuk mengurangkan isu -isu ini, jurutera terus meneroka reka bentuk litar yang lebih cekap.Strategi termasuk menggunakan teknologi pintu masuk logik yang lebih cepat, mengoptimumkan susun atur litar untuk memendekkan panjang laluan, dan membangunkan teknologi canggih seperti penambah bawa untuk meminimumkan kelewatan dalam penyebaran bawa.

Penambah penuh digunakan secara meluas dalam logik digital, berharga untuk fleksibiliti dan kecekapan mereka, menjadikannya pusat kepada banyak tugas pengkomputeran dan pemprosesan data.Permohonan mereka merangkumi operasi aritmetik asas kepada pemprosesan isyarat kompleks dan kawalan sistem.Berikut adalah pandangan terperinci di beberapa bidang utama di mana penambah penuh adalah penting.

Litar aritmetik

Salah satu penggunaan yang paling mudah untuk penambah penuh adalah dalam litar aritmetik di mana mereka melakukan penambahan binari.Terutama penting dalam penambahan nombor berbilang bit, penambah penuh menguruskan urutan binari yang lebih lama melalui cascading.Dalam susunan ini, setiap penambah penuh mengendalikan penambahan untuk kedudukan bitnya dan bawa dari bit yang lebih rendah, kemudian lulus bawa baru ke penambah penuh bit seterusnya yang lebih tinggi.Cascade ini membolehkan penambahan multi-bit yang komprehensif merentasi pelbagai digit.

Pemprosesan data

Penambah penuh juga memainkan peranan penting dalam tugas pemprosesan data canggih seperti pemprosesan isyarat digital (DSP) untuk penapisan dan transformasi Fourier, di mana operasi aritmetik yang tepat dan cepat diperlukan.Di samping itu, dalam bidang keselamatan maklumat, termasuk penyulitan data dan algoritma pengesanan ralat dan pembetulan seperti pemeriksaan pariti dan pemeriksaan kod redundansi kitaran (CRC), penambah penuh adalah penting untuk melaksanakan operasi bit penting.

Kaunter

Dalam kaunter digital, penambah penuh sangat diperlukan untuk melaksanakan kedua -dua fungsi kenaikan dan penurunan, terutamanya dalam kaunter modular dan segerak.Mereka mengurus dengan tepat membawa dan meminjam untuk memastikan pengiraan yang tepat.

Multiplexers (MUX) dan Demultiplexers (Demux)

Dalam multiplexers dan demultiplexers, penambah penuh memainkan peranan penting dalam pemilihan saluran dan pengagihan data.Mereka mengambil bahagian dalam logik yang menentukan saluran mana yang digunakan untuk input dan output data, membuat keputusan berdasarkan isyarat kawalan logik.

Teknologi memori

Dalam alamat memori, penambah penuh membantu menjana isyarat alamat untuk mengakses lokasi memori secara dinamik.Ini amat penting dalam memori akses rawak dinamik (DRAM) dan sistem storan lain, di mana penambah penuh menyokong pengiraan alamat kompleks untuk meningkatkan kecekapan akses memori.

Unit Logik Aritmetik (ALU)

Akhirnya, sebagai komponen asas unit logik aritmetik dalam mikropemproses dan pemproses isyarat digital, penambah penuh adalah penting.ALU mengendalikan semua operasi aritmetik dan logik, dengan penambah penuh memastikan data diproses dengan cepat dan tepat.

Penambah penuh boleh dibina menggunakan pelbagai pintu logik dan konfigurasi.Di sini, kami meneroka empat pelaksanaan yang berbeza, menonjolkan persediaan dan nuansa operasi mereka.

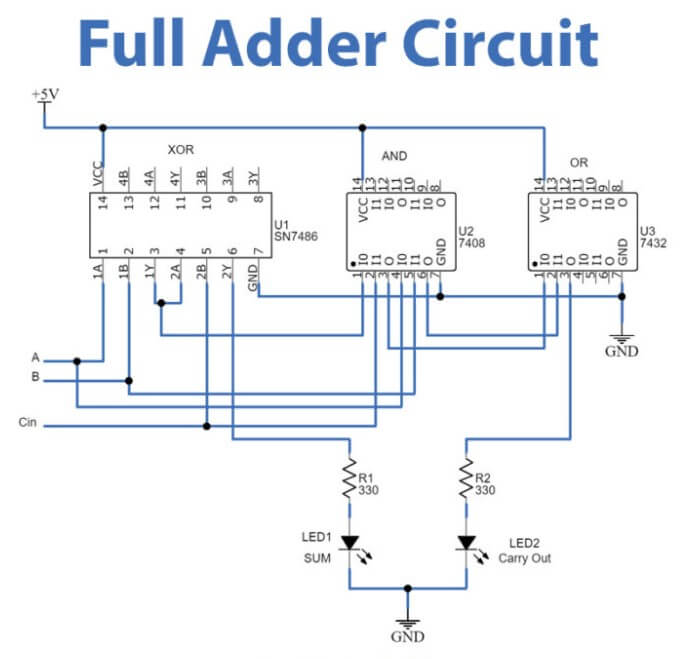

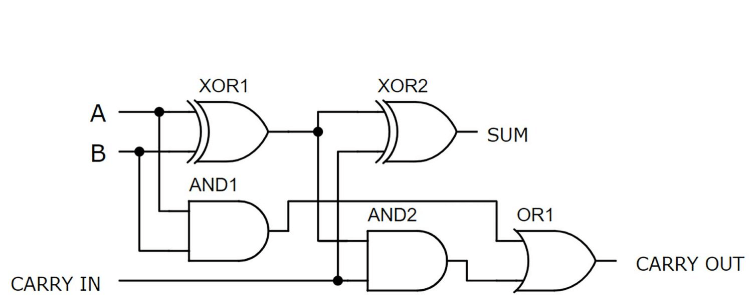

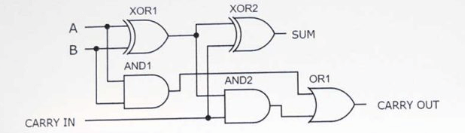

Penambah penuh dibina dengan XOR, dan, dan atau pintu gerbang

Rajah 6: Penambah penuh dibina dengan XOR, dan, dan atau pintu logik

Contoh ini mempamerkan penambah penuh yang dibina di atas papan roti menggunakan transistor diskret.Konfigurasi ini terdiri daripada lima pintu logik: dua pintu XOR, dua dan pintu, dan satu atau pintu, memerlukan sejumlah 21 transistor.Input A dan B disambungkan ke kiri atas papan roti, menerima bekalan +5V.Input ini dikawal menggunakan dua suis togol.Dua LED di sebelah kiri atas menunjukkan keadaan input A dan B, manakala dua LED di sebelah kanan memaparkan output.Resistor yang digunakan dalam litar adalah semua ohm 2.2k.Apabila input A dan B dihidupkan dan dibawa masuk, output menunjukkan nilai binari 10, yang mewakili jumlah 2 (1 + 1 + 0 = 10).Gerbang XOR, yang dibina dengan 12 transistor pertama, mengendalikan penjumlahan utama, manakala bahagian bawah papan roti mengandungi dan atau atau pintu untuk operasi membawa, pendawaian berkod warna meningkatkan kejelasan dan penyelesaian masalah.

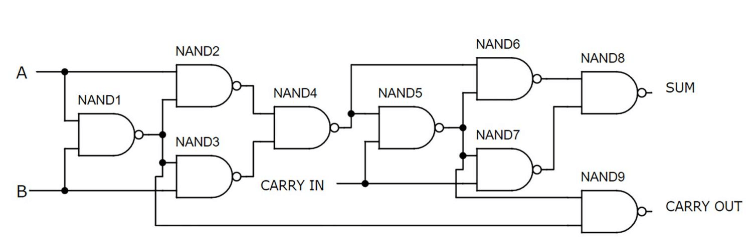

Penambah penuh menggunakan pintu gerbang

Rajah 7: Penambah penuh menggunakan pintu gerbang

Penambah penuh ini menggunakan sembilan pintu NAND, dengan setiap pintu dibuat dari dua transistor, berjumlah 18 transistor.Kaedah ini adalah antara cara yang paling mudah dan paling berkesan untuk membina penambah penuh menggunakan komponen diskret.Semua pintu dipasang di bahagian atas papan roti, manakala suis menduduki bahagian bawah.Fungsi litar ditunjukkan dengan input A dan B pada dan dibawa masuk, menghasilkan nilai binari output 10, bersamaan dengan perpuluhan 2.

Penambah penuh dengan gerbang atau pintu

Rajah 8: penambah penuh dengan gerbang atau pintu

Dibina dengan sembilan atau pintu, masing -masing memerlukan dua transistor, persediaan ini juga menggunakan 18 transistor secara keseluruhan.Membina penambah penuh dengan Gates Nor menawarkan alternatif yang baik tetapi melibatkan pendawaian yang lebih kompleks berbanding dengan pintu gerbang.Setiap transistor di pintu gerbang NOR didasarkan, dengan pengumpul yang dihubungkan dengan wayar jumper oren untuk memastikan pendawaian yang kemas dan teratur.Konfigurasi ini ditunjukkan dengan input A dan B diaktifkan dan dibawa masuk, yang membawa kepada output di mana bawaan aktif dan jumlahnya dimatikan.

Sepanjang penerokaan teknologi penambah ini, dari separuh asas penambah ke reka bentuk penambah penuh yang canggih, jelas bahawa komponen -komponen ini adalah asas kepada kemajuan elektronik digital.Ciri -ciri operasi dan contoh pelaksanaan memberikan garis bawah fleksibiliti dan kecekapan penambah dalam pelbagai tetapan pengiraan.Dengan mengkaji struktur dan fungsi penambah, terutamanya melalui jadual kebenaran mereka dan persamaan ciri, kita mendapat pandangan berharga ke dalam keupayaan dan kekangan mereka.Pengetahuan ini penting dalam memajukan reka bentuk sistem pengkomputeran yang lebih cekap dan lebih cepat.Pada akhirnya, penambah bukan sahaja memudahkan pengiraan binari kompleks tetapi juga membolehkan percambahan teknologi di kawasan yang pelbagai seperti pemprosesan data, peruntukan memori, dan pemprosesan isyarat digital.Memandangkan teknologi digital berkembang, penghalusan dan inovasi yang berterusan dalam reka bentuk penambah akan terus menjadi asas dalam pembangunan seni bina pengiraan yang lebih maju, memastikan bahawa komponen asas ini kekal di tengah -tengah reka bentuk dan pelaksanaan sistem digital.

Soalan Lazim [Soalan Lazim]

1. Apakah litar penambah penuh?

Penambah penuh adalah litar digital yang menambah tiga bit binari untuk menghasilkan jumlah dan output bawa.Ia direka untuk mengendalikan penambahan tiga input: dua bit penting dan satu bit dibawa dari tambahan sebelumnya.Ini membolehkan ia digunakan dalam peringkat berturut-turut untuk menambah nombor binari berbilang bit.

2. Berapa banyak dan, atau, xor secara penuh penambah?

Penambah penuh yang biasa mengandungi:

Dua pintu XOR untuk menjana jumlahnya.

Dua dan pintu untuk menyumbang kepada pengiraan yang dibawa.

Satu atau pintu untuk memuktamadkan output pembawa.

3. Apakah input membawa secara penuh?

Input membawa (CIN) dalam penambah penuh adalah bit membawa dari penambahan bit penting yang lebih rendah sebelumnya dalam penambahan binari multi-bit.Ia membolehkan penambah penuh untuk mempertimbangkan bawaan sebelumnya apabila mengira jumlah semasa dan pembawa baru.

4. Mengapa menggunakan penambah penuh dan bukannya setengah penambah?

Penambah penuh digunakan bukannya setengah penambah kerana ia boleh menambah tiga bit (termasuk bawa dari penambahan sebelumnya), menjadikannya sesuai untuk berantai bersama untuk menambah nombor berbilang bit.Tambahan setengah hanya boleh menambah dua bit dan tidak mempunyai peruntukan untuk dibawa masuk, yang menghadkan penggunaannya kepada bentuk tambahan yang paling mudah tanpa penyebaran bawaan.